- 2進数接頭辞 %0110, 0b0110, 4'b0110

- 16進数接頭辞 $89ab, 0x89ab, 16'h89ab

- active low, negative logic, 負論理

- address bus

- bank 切り換え

- bg, background

- CE, chip enable / CS, chip select

- CIC

- CIRAM

- charcter RAM

- charcter ROM

- CHR

- CHR A13# [誤用]

- CHR-RAM

- CPU CLK [誤用]

- CPU M2 [俗語?]

- CPU PHI2, φ2

- CPU R/W

- CRC

- data bus

- DIP, dual inline package

- EPROM

- EEPROM

- flash ROM [俗語]

- flash memory

- flash memory [俗語]

- high Z, hiZ, high-impedance

- mask ROM

- memory map

- mirror

- mirror H/V, VRAM mirror, CIRAM mirror

- nametable

- NES, Nintendo Entertainment System

- NES, ネス [俗語]

- OAM, object attribute memory

- object

- OE, output enable

- pinout

- PPU A13# [誤用]

- PPU RD#, PPU WR#

- PRG

- PRG/CHR A17 .. A0 [俗語]

- PRG RAM

- program [動詞]

- program ROM

- scroll

- serial EEPROM

- sprite

- sprite RAM, sprite attribute

- system VRAM, 本体VRAM

- static RAM, SRAM

- tilemap

- TTL

- TTL [誤用]

- W-RAM

- WE, write enable

- work RAM

ソースコードで 0 と 1 で2進数を表記するための約束事。それに転じて、仕様の表記にも用いられる。

現在では用途が限られてしまうが、ファミコンでは 8bit のデータバスを持ち、レジスタには各 bit にそれぞれ別の機能を持たせている。このため、区別しやすくするために2進数表記が好まれる場面が存在する。

現在では用途が限られてしまうが、ファミコンでは 8bit のデータバスを持ち、レジスタには各 bit にそれぞれ別の機能を持たせている。このため、区別しやすくするために2進数表記が好まれる場面が存在する。

- % は 6800 を祖先とする Motorola 系のアセンブラで使用する。

- 0b は C 言語やそれに派生する言語で 0x のように定義されたもの。b は binary の略だと思われる。

- 4'b はハードウェア記述言語で桁数まで明記できるようにしたもの。

ソースコードで16進数を表記するためのもので、2進数と目的は同じ。

- $ は 6800 系

- 0x は C 系

- 16'h は HDL 系, (16 が桁数, h が hex → 16進数の意味)

address bus, data bus を制御する CS, CE, WE, OE などは low レベルを有効, high レベルを無効とした反転信号を用い、負論理としている。

このため反転の意味合いは文字の上にバーを挿入するのが正しい表記とするが、コンピュータではバーの挿入が出来ない場合は端子名の前後に記号を付けることで代用している。

記号には ~, #, -, *, n など様々あり統一されていない。

SRAM の CS2 のように制御信号が正論理の場合は何も付けない。強調したい場合は + を付ける。

このため反転の意味合いは文字の上にバーを挿入するのが正しい表記とするが、コンピュータではバーの挿入が出来ない場合は端子名の前後に記号を付けることで代用している。

記号には ~, #, -, *, n など様々あり統一されていない。

SRAM の CS2 のように制御信号が正論理の場合は何も付けない。強調したい場合は + を付ける。

CPU, PPU の各プロセッサがどのアドレスを参照しているかを出力する信号で多ビットをまとめて bus と呼ぶ。

この wiki では CPU のアドレス表記の接頭辞は 6800 系の $ を使用し、 PPU のアドレス表記は CPU に無関係ということで 0x を使用する。

この wiki では CPU のアドレス表記の接頭辞は 6800 系の $ を使用し、 PPU のアドレス表記は CPU に無関係ということで 0x を使用する。

nametable を参照して 8x8 pixel の charcter を敷き詰めた4画面分の仮想画面。正方形の画像を敷き詰めるので tile とも呼ばれる(風呂場の床のタイルと同じ)。object と異なり、横並び制限がないので大きいボスを表示するときにも使われる。これを使うとユーザーにとっての背景が真っ黒になるのはちょっと寂しい。

属性としては background ではなく foreground にもできるが bg という言葉になっているのはちょっともどかしい。

属性としては background ではなく foreground にもできるが bg という言葉になっているのはちょっともどかしい。

ROM と RAM の制御端子で、CPU がアドレスを有効な場合を示す信号として入力する。CE は ROM で、 CS が RAM に多いが役割は同じで名称が別になっている理由は筆者は知らない。

OE とペアで利用して、OE だけで動かす場合などは CE は GND に接続されていることも多い。使わないからと言って何も接続しないとちゃんと動かない。

OE とペアで利用して、OE だけで動かす場合などは CE は GND に接続されていることも多い。使わないからと言って何も接続しないとちゃんと動かない。

NES カートリッジについているセキュリティチップ。契約をしていない会社などから勝手にゲームソフトを作られないようにした仕組みだが、その割には結構な数が作られている。IC を作られないようにするというかは、勝手に作った事実をもとに訴えやすくする目的のようだ。

ファミコンにはついていないが、スーパーファミコンにはついている。

ファミコンにはついていないが、スーパーファミコンにはついている。

Charcter ROM の代わりに入っている RAM で PPU address 0x0000-0x1fff に配置する。RAM の場合は CPU の Program から RAM へ charcter data を転送する。charcter data は冗長性が高いので圧縮率が高く、ROM を2つ作らなくて良いので容易な変更が可能、キャラを徐々に消すエフェクトをかけることができるなどの特徴を持つ。

その反面、データの転送に時間がかかることや容量の少なさもあって描画途中のバンク切り替えに不向き。UNROM, SNROM, SGROM などでは charcter RAM のバンク切り替えができない。

ファミコンとNEOGEO以外の家庭用ゲーム機では Charcter RAM を本体に持つので外付けすることはない。

その反面、データの転送に時間がかかることや容量の少なさもあって描画途中のバンク切り替えに不向き。UNROM, SNROM, SGROM などでは charcter RAM のバンク切り替えができない。

ファミコンとNEOGEO以外の家庭用ゲーム機では Charcter RAM を本体に持つので外付けすることはない。

名の通り、 charcter data が入っている ROM で、 PPU address 0x0000-0x1fff に配置されることが普通である。手の込んだメモリコントローラではこの ROM を nametable に使用することもある。ただし利用例が少なく Charcter data 兼用ということでそういうものも便宜上 Charcter ROM とされている。

この言葉は使ってはいけない。

Charcter ROM を enable する目的の端子で使われる誤記。

PPU の A13 は L のときに charcter data, H のときにそれ以外のデバイスを使用する。 Charcter ROM の CE# には PPU A13 (正論理) を接続するのが普通だが、論理否定の記号と制御端子によくつく信号を混合しているのが原因。

紛らわしいことに PPU の A13# という本当に反転した信号もカートリッジ端子には存在する。

Charcter ROM を enable する目的の端子で使われる誤記。

PPU の A13 は L のときに charcter data, H のときにそれ以外のデバイスを使用する。 Charcter ROM の CE# には PPU A13 (正論理) を接続するのが普通だが、論理否定の記号と制御端子によくつく信号を混合しているのが原因。

紛らわしいことに PPU の A13# という本当に反転した信号もカートリッジ端子には存在する。

→ CPU φ2

英語圏の解析文書でよく用いられる言葉で、φ2 と同意とされている。ただし、6502 のφ2 と比較して、 2A03 のこの端子は出力が若干遅いので 2A03 の φ2 相当という意味で M2 と再定義している場合もある。

Z80 には M1 と呼ばれる opcode fetch などを外部に知らせる信号があるが、関連性はない。

英語圏の解析文書でよく用いられる言葉で、φ2 と同意とされている。ただし、6502 のφ2 と比較して、 2A03 のこの端子は出力が若干遅いので 2A03 の φ2 相当という意味で M2 と再定義している場合もある。

Z80 には M1 と呼ばれる opcode fetch などを外部に知らせる信号があるが、関連性はない。

6502 のメモリサイクルで M2 とも呼ばれる。 read, write 時のバスの有効タイミングを決定したり、 CPU の動作時間を計測するためにメモリコントローラ内部のタイマーのクロックとしても使われる。

65CE02 の datasheet の timing diagram.

φ0が CPU への master clock で、φ1がφ0から位相を反転し遅延を加えたもの。φ2はφ1から位相を反転し遅延を加えたもの。

φ2の期間について説明する。

65CE02 の datasheet の timing diagram.

φ0が CPU への master clock で、φ1がφ0から位相を反転し遅延を加えたもの。φ2はφ1から位相を反転し遅延を加えたもの。

φ2の期間について説明する。

- L の期間は R/W, Address bus, data bus に不安定な期間があるので、外部のバスに対して無効になる。

- L→H には R/W と A15:0 の出力が安定しているのでここからバスが有効になる。

- H の期間は有効になったデバイスが L になるまでにデータ出力を準備する期間となる。

- H→L

- read:CPU がデータを取り込む

- write:対応するデバイスがデータを取り込む

- 再び Lの期間に戻るが、データ出力の遅延が残っていたり、途中で出力を停めるので不安定期間となる。

high が read, low が write をさす。PPU の RD# と WR# を一緒にしたものだが、φ2 と組み合わせて CE#, OE#, WE# を作る必要がありメモリへの接続がやりづらい。

文書によっては R/W の W の上に線がつくので R/~W などとする場合がある。

文書によっては R/W の W の上に線がつくので R/~W などとする場合がある。

データの誤り検出。ROM データのチェックサムとして CRC32 を用いることが多い。誤検出も多いと言うことで SHA1SUM なども使われるが、8文字で記述できるのは便利なので根強い人気を持つ。

CPU, PPU の各プロセッサがデータを扱う端子で、多 bit をまとめて bus と呼ぶまでは address bus と同じ。

data には read と write があり、 read 時は参照アドレスが担当するデバイスがデータを出力し、CPU が取り込む。write 時は CPU がデータを出力し、担当デバイスが取り込む。このようにプロセッサにとって出力と入力を兼ねており、そのバスがつながっているデバイスは CPU も含めて 1 つが出力することが基本である。

複数のデバイスが同時にデータを出力するとバス衝突となりデータの内容が不安定になる。

data には read と write があり、 read 時は参照アドレスが担当するデバイスがデータを出力し、CPU が取り込む。write 時は CPU がデータを出力し、担当デバイスが取り込む。このようにプロセッサにとって出力と入力を兼ねており、そのバスがつながっているデバイスは CPU も含めて 1 つが出力することが基本である。

複数のデバイスが同時にデータを出力するとバス衝突となりデータの内容が不安定になる。

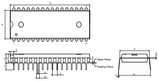

ピンとピンの距離が 2.54mm で一般的な IC のイメージと言えばこれが出てくるかもしれない。1990年頃までは一般的に使われていたが、電子回路の高密度化にともなって、プリント基板では 2.54mm は相対的に大きくなり、穴を開ける必要もあり需要は低下。特にピン数が多いものでは避けられる傾向にあって、現在は 74LS の IC や EEPROM のみ現行品ということもある。

その反面、ブレッドボードなど試作の分野などアマチュアには根強い人気を持つ。ファミコンに関するプリント基板はやはり1990年頃までは DIP 部品ばかりだが、それ以降は表面実装の部品が使われ始めている。

DIP パッケージと表記すると AV ビデオ(アダルトビデオビデオ)みたいに単語が重複するので略語の意味をしっているとかっこわるく聞こえるから困る。

高電圧(12V) で書き込みを行う ROM で、窓に紫外線を照射することでデータの消去が行える。データの消去には1時間程度の時間がかかるので、頻繁な書き換えには不向き。

ファミコン時代には flash memory が存在しなかったので開発者達は EPROM の書き込みに関しては ROM を何セットも用意して、長篠の合戦における火縄銃のように消去ができた ROM から随時書き込みをおこなったと見られる。

ファミコン時代には flash memory が存在しなかったので開発者達は EPROM の書き込みに関しては ROM を何セットも用意して、長篠の合戦における火縄銃のように消去ができた ROM から随時書き込みをおこなったと見られる。

ファミコンのカートリッジの ROM から置き換えることの出来る flash memory. 16 bit から 19 bit のアドレスバスと 8bit のデータバスを持ち、5V で動作する。

シリアル EEPROM と比較してパラレル EEPROM と称されることもある。

DIP 形状のものは 1990 年代中頃から普及し、パソコンの BIOS に用いられている。現在でもパソコンの BIOS に使われているが、形状が表面実装になっていたり、3.3V 動作なのでファミコンカートリッジの転用は理論上可能。でも手間がかかる。

シリアル EEPROM と比較してパラレル EEPROM と称されることもある。

DIP 形状のものは 1990 年代中頃から普及し、パソコンの BIOS に用いられている。現在でもパソコンの BIOS に使われているが、形状が表面実装になっていたり、3.3V 動作なのでファミコンカートリッジの転用は理論上可能。でも手間がかかる。

入力もしてない、出力もしてない状態。メモリデバイスでは CS# が high または OE# が high のときにデータバスの出力が hiZ となる。

CPU が read 時にそのアドレスが未定義(=なにも使わない)場合はデータバスが open 状態と呼ばれる。この場合は、read 時は不定値となるかプルアップがしてあればすべて high (8'hff) となる。

hiZ 状態になれる出力端子は high, low, hiZ の3つがでるということで tri-state とも呼ばれる。

CPU が read 時にそのアドレスが未定義(=なにも使わない)場合はデータバスが open 状態と呼ばれる。この場合は、read 時は不定値となるかプルアップがしてあればすべて high (8'hff) となる。

hiZ 状態になれる出力端子は high, low, hiZ の3つがでるということで tri-state とも呼ばれる。

CPU, PPU のアドレスにどのデバイス(ROM, RAM, その他レジスタ)を配置するかを定義するもの。ファミコンでは本体内部の RAM と各レジスタ以外は、カートリッジ側で設定できるのでカートリッジの配線によって異なる。

自由度の高さは豊富な拡張性をもたらした反面、仕様の乱立は混乱の原因となっている。

memory map では CPU, PPU の各プロセッサがマスターとなり、カートリッジ内部の program ROM, charcter ROM はその中の1デバイスであることを覚えると理解が進みやすい。

自由度の高さは豊富な拡張性をもたらした反面、仕様の乱立は混乱の原因となっている。

memory map では CPU, PPU の各プロセッサがマスターとなり、カートリッジ内部の program ROM, charcter ROM はその中の1デバイスであることを覚えると理解が進みやすい。

memory map 内部で定義されたデータが一定の address を越えると同内容のデータで繰り返される現象。例えば CPU address $0000-$1fff は本体 RAM として定義されているが、RAM の容量は 0x800 byte のため、0x800 byte ごとに 4 度同じ内容が繰り返されている。先頭の $0000-$07ff をRAM本体とし、残りの $0800-$1fff ミラー領域と呼ばれることがある。

大きめに定義したメモリ領域はあるものの、実際につながれたデバイスがそれより少ないと上位アドレスビットが存在しない。 上位アドレスbitを完全にデコードせずに CE に接続すると、この状態が発生する。

上記の例では CPU からは A15:0 が来ているが、 RAM につながるのは A15:13 が CS 信号としてデコードされ、 A10:0 がアドレスバスとして直接 RAM につながり、 A12:11 が未接続となる。

将来的な拡張で足りない物理メモリ容量が拡張されることもあるので、 mirror 領域にはアクセスしないようにルールを決めている場合も多い。

大きめに定義したメモリ領域はあるものの、実際につながれたデバイスがそれより少ないと上位アドレスビットが存在しない。 上位アドレスbitを完全にデコードせずに CE に接続すると、この状態が発生する。

上記の例では CPU からは A15:0 が来ているが、 RAM につながるのは A15:13 が CS 信号としてデコードされ、 A10:0 がアドレスバスとして直接 RAM につながり、 A12:11 が未接続となる。

将来的な拡張で足りない物理メモリ容量が拡張されることもあるので、 mirror 領域にはアクセスしないようにルールを決めている場合も多い。

nametable の領域は 0x1000 byte として定義されているものの、本体の VRAM の容量が 0x800 byte なので mirror が発生する。nametable ではその mirror を利用して nametable を縦長 (vertical) にするか横長 (horizonal) にするか選択できる。

配線としてはカートリッジの VRAM A10 に PPU A10 か A11 を接続することで H/V を選択できる。ソフトによっては 0x400 byte だけ使うという需要もあるので low か high を接続することもある。それに転じて VRAM A10 への配線方法を mirroring とか VRAM mirror とか呼ばれることがある。

配線としてはカートリッジの VRAM A10 に PPU A10 か A11 を接続することで H/V を選択できる。ソフトによっては 0x400 byte だけ使うという需要もあるので low か high を接続することもある。それに転じて VRAM A10 への配線方法を mirroring とか VRAM mirror とか呼ばれることがある。

bg を構成する色情報、キャラ情報などを並べたテーブル。

PPU の address 0x2000-0x2fff に使用され基本的に本体の VRAM を使う。

1画面分の nametable は 0x400 byte なので、論理的には4画面分を持つ。なお本体の VRAM の容量は 0x800 byte なので mirror が発生する。

PPU の address 0x2000-0x2fff に使用され基本的に本体の VRAM を使う。

1画面分の nametable は 0x400 byte なので、論理的には4画面分を持つ。なお本体の VRAM の容量は 0x800 byte なので mirror が発生する。

日本国外でのファミコン相当の家庭用ゲーム機。72pin のカートリッジコネクタを持ち、コントローラを取り外しできるところが特徴。コントローラにマイクがないことは外見から広く認知されているが、カートリッジへのサウンド入出力端子もないので拡張音源という概念は無改造では存在できない。

米国では普及したものの、それ以外の国では普及しなかったらしい。

米国では普及したものの、それ以外の国では普及しなかったらしい。

sprite ともよばれ、8x8 pixel または 16x8 pixel のキャラを任意の位置に表示させる仕組み。object の attribute は OAM だが、 charcter は PPU の外部バスで scroll と共用している。

1 scanline 中で 64 pixel 以上は描画できないので横並び制限が厳しいと言われている。

1 scanline 中で 64 pixel 以上は描画できないので横並び制限が厳しいと言われている。

CPU が data を read する場合に有効となる端子。CS/CE が address を担当して、 OE が data を担当しているとすれば理解しやすい。

SRAM は OE が L でも WE が L だと write として受け付ける、一種の矛盾した実装となっているが、 flash memory ではこの矛盾はおきないようになっている。

SRAM は OE が L でも WE が L だと write として受け付ける、一種の矛盾した実装となっているが、 flash memory ではこの矛盾はおきないようになっている。

→ CHR A13#

本来は PPU A13# は PPU の address bit 13 を反転したもので、この言葉自体は間違いではないが、 PPU A13 (非反転)を制御信号の記号として混同していることがある。

本来は PPU A13# は PPU の address bit 13 を反転したもので、この言葉自体は間違いではないが、 PPU A13 (非反転)を制御信号の記号として混同していることがある。

RD# は read するとき, WR# は write するときに使用する出力信号。

OE# は RD#, WE# は WR# に配線するのが一般的。

RD#, WR# は同時に L になりうるが、メモリへの接続はやりやすい。

OE# は RD#, WE# は WR# に配線するのが一般的。

RD#, WR# は同時に L になりうるが、メモリへの接続はやりやすい。

Program/Charcter ROM のアドレスバスの端子を表記するためによく使われる。

ROM 単体としては A17 (最上位ビット, MSB) から A0 (最下位ビット, LSB) を表記するのは間違っていないが、配線ではバンク切り替えをするbitを Program/Charcter ROM Ax で表記し、バンク切り替えをしない bit を CPU/PPU An で表記した方が混乱が減る。

上記の理由から ROM 単体の pinout を記載する場合は PRG/CHR Ax という接頭辞は付けずに単に Ax と記載する方が情報の精度があがるので俗語とした。

ROM 単体としては A17 (最上位ビット, MSB) から A0 (最下位ビット, LSB) を表記するのは間違っていないが、配線ではバンク切り替えをするbitを Program/Charcter ROM Ax で表記し、バンク切り替えをしない bit を CPU/PPU An で表記した方が混乱が減る。

上記の理由から ROM 単体の pinout を記載する場合は PRG/CHR Ax という接頭辞は付けずに単に Ax と記載する方が情報の精度があがるので俗語とした。

EPROM や flash memory への不揮発データ書き込みは英語では program と呼ばれて、 RAM への書き込みは write と区別される。日本語では両方とも書き込み - ライトと一緒にされてしまっている。

カートリッジ内部の CPU に接続される ROM で必ず存在する。

名称は program ROM だが CPU が使うプログラムの他にデータも入っている。charcter 用途の memory が RAM の場合はキャラクタデータも入っている。その場合は圧縮されていることがよくある。

名称は program ROM だが CPU が使うプログラムの他にデータも入っている。charcter 用途の memory が RAM の場合はキャラクタデータも入っている。その場合は圧縮されていることがよくある。

本体内部で大半は PPU のバスが接続された 0x800 byte の RAM.

A10 と CS# はカートリッジからの出力を受け付けるようになっていて、大半のカートリッジは PPU address 0x2000-0x2fff に設定して、 nametable とするのが普通。

それ以外としては本体 VRAM を使用せずに 0x2000-0x2fff を Charcter ROM に割り当てたり、0x2000-0x2fff をカートリッジ内部の RAM に割り当てることもできる。この場合は nametable 領域 0x1000 byte をフル活用できるので 4 screen mode と呼ばれる状態になる。

それとは別にキャラクタ領域の 0x0000-0x1fff を本体 VRAM に割り当てることも理論上はできるが、キャラクタとしての 0x800 byte では制限が多くて使いにくいようだ。

A10 と CS# はカートリッジからの出力を受け付けるようになっていて、大半のカートリッジは PPU address 0x2000-0x2fff に設定して、 nametable とするのが普通。

それ以外としては本体 VRAM を使用せずに 0x2000-0x2fff を Charcter ROM に割り当てたり、0x2000-0x2fff をカートリッジ内部の RAM に割り当てることもできる。この場合は nametable 領域 0x1000 byte をフル活用できるので 4 screen mode と呼ばれる状態になる。

それとは別にキャラクタ領域の 0x0000-0x1fff を本体 VRAM に割り当てることも理論上はできるが、キャラクタとしての 0x800 byte では制限が多くて使いにくいようだ。

高速なアクセスと比較的小容量が特徴の RAM で、バッテリーバックアップが可能。

ファミコンでは RAM アダプタの DRAM 以外は基本的にほとんどが SRAM。

SRAM 単体ではなくメモリコントローラの中に内蔵している場合もあり、その場合はメモリコントローラに電池をつなぐ。

ファミコンでは RAM アダプタの DRAM 以外は基本的にほとんどが SRAM。

SRAM 単体ではなくメモリコントローラの中に内蔵している場合もあり、その場合はメモリコントローラに電池をつなぐ。

汎用ロジックIC 74LS シリーズの IC とその信号規格を指す。当時としては高速動作をして壊れにくいことで大量に使用された。その後、 CMOS を利用した 74HC シリーズが台頭するが、74LS と 74HC は混在して使ってはいけないことになっている。(混在するなら 74HCT シリーズを使う)

狭義では 74LS シリーズだけをさすが、DIP 形状の汎用ロジックIC を使う場合は 4000 シリーズでも 74HC シリーズでも TTL と言う人が一定の世代で設計をしていた方々に多い。

言いやすいのは認めるが、紛らわしいのでその意味では使ってはいけない。

秋月電子のロジックIC(TTL)カテゴリには厳密な TTL は現在1つも売ってないが、誤用での TTL はいくつか売っている。

http://akizukidenshi.com/catalog/c/clogic/

言いやすいのは認めるが、紛らわしいのでその意味では使ってはいけない。

秋月電子のロジックIC(TTL)カテゴリには厳密な TTL は現在1つも売ってないが、誤用での TTL はいくつか売っている。

http://akizukidenshi.com/catalog/c/clogic/